什么是澜起科技DDR5内存接口芯片?

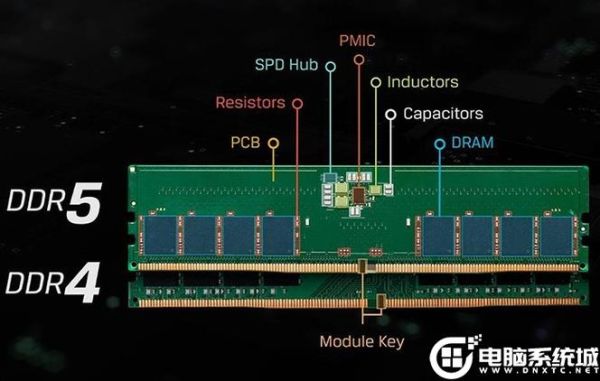

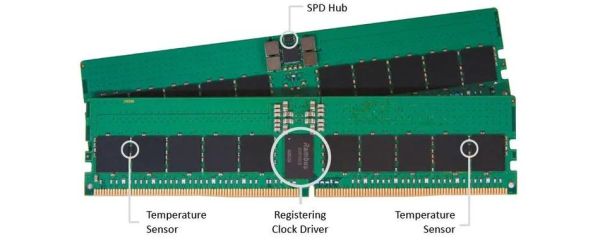

澜起科技DDR5内存接口芯片(Memory Interface Chip,简称MIC)是专为新一代DDR5内存模组设计的核心逻辑器件,位于CPU与DRAM颗粒之间,承担信号完整性、时序校准、功耗管理三大职能。它通过高速SerDes通道与CPU通信,再以并行方式驱动DRAM,实现更高带宽、更低延迟、更低功耗的内存子系统。

DDR5与DDR4到底差在哪?

1. 带宽与频率

DDR4主流频率止步于3200 MT/s,而DDR5起步即4800 MT/s,未来可扩展至8400 MT/s以上。澜起科技第二代DDR5 RCD(Registering Clock Driver)已支持6400 MT/s,单条模组带宽提升近一倍。

2. 容量密度

DDR4单Die更大16 Gb,单条DIMM常见32 GB;DDR5单Die可达64 Gb,配合3DS堆叠技术,单条可做到256 GB。澜起科技的DB(Data Buffer)芯片支持多Rank并行,进一步释放大容量优势。

---澜起科技芯片如何提升系统稳定性?

信号完整性黑科技

- FFE/DFE均衡器:在RCD内部集成前向反馈与判决反馈均衡,补偿PCB与连接器损耗。

- 动态ODT:根据读写方向实时调整终端电阻,减少信号反射。

时序校准自动化

传统方案需要BIOS手动训练;澜起科技内置PVT(Process/Voltage/Temperature)传感器,在系统启动时自动完成Write Leveling与Read Gate训练,缩短开机时间。

---功耗管理:DDR5为何更省电?

1. 双通道32-bit子通道

DDR5把64-bit总线拆成两个32-bit子通道,降低单端信号切换电流,配合澜起科技的细粒度时钟门控,待机功耗下降30%。

2. 1.1 V VDD与PMIC集成

DDR4需主板供电,电压1.2 V;DDR5将PMIC直接封装在DIMM上,电压降至1.1 V,澜起科技的PMIC芯片支持多相Buck,瞬态响应更快。

常见疑问解答

问:DDR5内存接口芯片会不会增加延迟?

答:虽然增加一级逻辑,但澜起科技通过管线化设计与预取算法,将额外延迟控制在1-2个时钟周期,远低于带宽提升带来的收益。

问:旧主板能否通过升级BIOS支持DDR5?

答:不能。DDR5针脚从288增加到288+10(电源管理),物理不兼容,必须更换支持DDR5的CPU与主板。

---企业级应用场景

云计算与AI训练

阿里云第七代ECS已采用澜起科技DDR5 RCD+DB组合,单节点内存带宽提升50%,ResNet50训练时间缩短18%。

高频交易

某头部券商部署DDR5后,行情解码延迟从87 ns降至63 ns,撮合引擎吞吐量提升22%。

---未来路线图

澜起科技第三代DDR5芯片将于2025年量产,支持CXL 2.0内存扩展,单通道带宽突破100 GB/s,并引入片上ECC,进一步降低服务器RAS成本。

评论列表