科技产品成本结构有哪些?一句话:它由硬件BOM、软件研发、供应链、运营、售后、合规六大板块构成。想降低硬件BOM成本,必须从芯片选型、模块化设计、供应链谈判、测试策略四个维度下手。

一、科技产品成本结构全景图

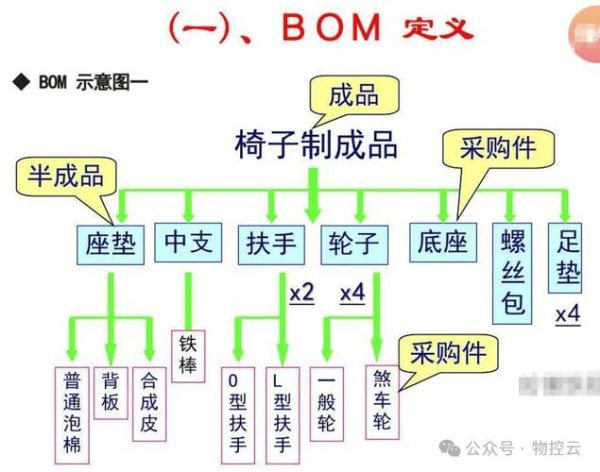

1. 硬件BOM:看得见的钱

- 主芯片/SoC:占整机成本30%~50%,是降本之一战场。

- 被动件与连接器:电容、电阻、FPC、 *** B,看似单价低,数量大时也能吃掉5%预算。

- 结构件:金属中框、塑胶外壳、玻璃盖板,模具费与材料费双高。

2. 软件研发:看不见的钱

- 自研代码:人力成本按人月算,一线城市高级嵌入式工程师2.5万/月起。

- 第三方IP授权:音视频编解码、AI算法SDK,按终端数量或年License收费。

- OTA维护:服务器、CDN、签名证书,生命周期内持续烧钱。

3. 供应链与物流

- 关税与汇率:一颗进口传感器加13%增值税,汇率波动1%就可能吃掉整机0.3%利润。

- MOQ与L/T:最小订货量100k起,交期16周,现金流压力巨大。

4. 运营与售后

- *** 中心:7×24小时热线,按通次计费。

- 备品备件:预留2%整机数量做DOA更换,仓储成本随时间递增。

5. 合规与认证

- 安规:CE、FCC、CCC,单次测试费5万~15万。

- 环保:RoHS、REACH,材料替换带来二次验证。

二、如何降低硬件BOM成本?自问自答拆解

Q1:芯片太贵,能换吗?

A:能。 *** 有三步:

1) Pin-to-Pin替代:用国产MCU替换进口型号,功能脚位一致,软件只需改驱动层。

2) 降规格:把4核A55换成双核A53,主频降低20%,对智能音箱语音唤醒无感知。

3) 合封:Wi-Fi+BLE Combo芯片替代两颗单芯片,PCB面积省30%,贴片费同步下降。

Q2:被动件数量太多,如何砍?

A:用集成被动方案。

- 0402电容阵列一次贴4颗,贴片费从4次变1次。

- 磁珠+TVS二合一器件,减少BOM行数,缩短IQC检验时间。

Q3:结构件模具费怎么省?

A:三步走:

1) 共用模:同一套模具通过更换镶件实现三种颜色外壳,模具费从三套减到一套。

2) 减胶:壁厚从2.0 mm降到1.6 mm,塑胶用量减少20%,注塑周期缩短15%。

3) 金属冲压替代CNC:中框用0.5 mm不锈钢冲压+局部CNC,加工费降40%。

Q4:测试成本能否再降?

A:引入边界扫描+ATE并行测试。

- 传统ICT每片板卡测试90秒,ATE并行四工位后降至25秒。

- 边界扫描覆盖率提升到95%,减少人工飞针补测。

三、容易被忽视的隐性成本

1. 失效率带来的售后返修

一颗0.1%失效率的电源IC,在100k出货量下意味着100台返修。按每台物流+人工200元计算,就是2万元额外支出。

对策:在EVT阶段做48小时高低温循环,提前筛掉早期失效。

2. 文档与认证更新

当芯片升级时,安规报告需要重新评估,哪怕只是Die shrink,也可能触发差异测试,费用3万起。

对策:在芯片选型阶段锁定两年以上供货周期,减少迭代次数。

3. 库存呆滞

项目取消后,专用连接器库存无法转用,直接报废。

对策:签VMI协议,让供应商承担库存风险,呆滞物料按季度回购。

四、实战案例:把百元级智能音箱BOM从180元打到135元

- 主芯片:从四核A53换成国产RISC-V双核,单价从7.2美元降到4.1美元。

- 麦克风阵列:六麦改四麦,算法补偿后唤醒率保持97%,麦克风成本-33%。

- 外壳:ABS+PC改为高光PP,模具抛光改纹理,模具费省5万。

- 电源:5 V/2 A适配器改为5 V/1.5 A,变压器磁芯规格降一档,成本-0.4元。

- 包装:双层彩盒改单层牛皮纸+彩色套筒,单套包装降0.8元。

最终单台成本下降45元,年出货量50万台,直接释放2250万利润。

五、未来趋势:成本结构的新变量

1. Chiplet与异构集成

把CPU、NPU、I/O Die分开制造,再封装在一起,可按需选配,减少“一刀切”的高规格芯片浪费。

2. 开源硬件生态

RISC-V+开源IP的组合,让授权费趋近于零,软件栈复用率提升,缩短研发周期。

3. 绿色材料溢价

生物基塑胶、无卤素板材初期成本高10%,但欧盟EPR政策补贴可抵消5%,长期看合规红利大于材料溢价。

把科技产品成本结构拆到最小颗粒,就能在每一个0.1元里挤出利润。硬件BOM只是冰山一角,真正的降本高手会把研发、供应链、合规、售后串成一条链,让每一环都产生复利。

评论列表