长电科技(JCET)是全球前三的OSAT厂商,很多工程师在选型时都会问:长电科技封装工艺有哪些?以及长电科技先进封装技术怎么样?下面用问答形式拆解产品手册,带你一次看懂。

(图片来源 *** ,侵删)

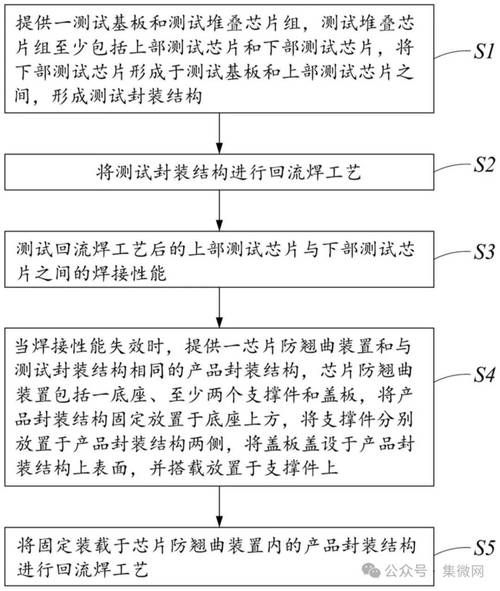

长电科技封装工艺有哪些?

翻开长电科技最新产品手册,可将其封装工艺按传统、先进、系统级三大维度梳理:

1. 传统封装

- QFN/DFN:脚位从32到256,厚度更低0.5 mm,适合MCU、PMIC。

- SOP/TSSOP:脚距0.5 mm,成本低,量大。

- TO/DO:功率器件散热好,耐压可到1200 V。

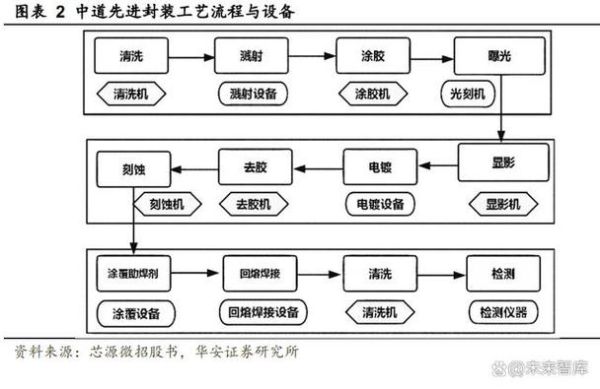

2. 先进封装

- FC-BGA:基板层数2-18层,更大封装尺寸65 mm×65 mm,支持HBM。

- FC-CSP:0.3 mm pitch,薄至0.55 mm,适合手机AP、RF。

- SiP:将射频、电源、存储整合,最小模组尺寸4 mm×4 mm。

- 2.5D/3D IC:TSV深宽比20:1,中介层线宽/线距2 µm/2 µm。

3. 系统级封装

- Antenna-in-Package:把天线、滤波器、PA合封,5G毫米波首选。

- Chiplet:支持Die-to-Die接口UCIe,功耗<0.5 pJ/bit。

长电科技先进封装技术怎么样?

要回答“怎么样”,先看性能、产能、可靠性三条硬指标。

性能指标

- 互连密度:FC-BGA 2-2 µm线宽/线距,已量产。

- 信号完整性:插入损耗<0.2 dB/mm@28 GHz。

- 热阻:θJC低至0.15 ℃/W,散热优势明显。

产能布局

- 江阴总部:月产FC-BGA 1.2亿颗。

- 韩国 *** CK:高端SiP专线,月产能8000万颗。

- 新加坡厂:2.5D/3D TSV产线,12吋晶圆月产能5万片。

可靠性验证

- HTOL:1000 h@125 ℃,失效率<10 ppm。

- TC:-55 ℃↔125 ℃循环1000次,无分层。

- HAST:96 h@130 ℃/85 %RH,通过JEDEC标准。

工程师最关心的五个细节问答

Q1:FC-BGA基板层数怎么选?

手册给出信号完整性仿真模板: - 8层以内:适合DDR4、PCIE3.0。 - 10-14层:DDR5、PCIE5.0。 - 16-18层:HBM3、AI加速器。

Q2:SiP模组里能放几颗Die?

官方案例: - 5G射频前端SiP可放PA×3+LNA×2+Switch×4+滤波器×6,厚度仅0.8 mm。

Q3:2.5D中介层更大尺寸?

目前量产65 mm×65 mm,下一代试产85 mm×85 mm,中介层厚度100 µm。

(图片来源 *** ,侵删)

Q4:Chiplet方案支持哪些接口?

已验证UCIe、BoW、OpenHBI,速率更高32 GT/s。

Q5:车规级封装通过哪些认证?

AEC-Q100 Grade 1、IATF 16949、ISO 26262 ASIL-D流程全部覆盖。

如何快速选型?

把手册里的选型矩阵提炼成三步:

- 先定封装类别:功率器件→TO/DO;高速芯片→FC-BGA;轻薄终端→FC-CSP。

- 再看脚数/尺寸:手册给出每类最小/更大封装尺寸与脚数对照表。

- 最后确认可靠性等级:消费电子、工业、车规三档一目了然。

价格与交期

手册未公开具体数字,但透露:

- 传统封装:交期4-6周,价格随脚数线性增加。

- 先进封装:交期8-12周,2.5D/3D需额外4周TSV加工。

- 紧急订单:可启动“绿色通道”,最快缩短30 %交期。

长电科技未来路线图

产品手册最后一页给出2024-2027技术节点:

(图片来源 *** ,侵删)

- 2024 Q4:量产3D IC 0.8 µm pitch。

- 2025 Q2:推出玻璃基板FC-BGA,线宽/线距1.5 µm。

- 2026 Q1:Chiplet异构集成,支持3D DRAM+HBM4。

- 2027:硅光共封,单通道112 Gbps PAM4。

通过拆解手册可见,长电科技在传统、先进、系统级三大维度均提供完整工艺菜单,性能、产能、可靠性均处于行业之一梯队。工程师只需按“封装类别→尺寸→可靠性”三步法即可快速锁定方案。

评论列表